Tri-gate nel dettaglio

Andiamo ad analizzare nel dettaglio la struttura dei nuovi transistor che andranno a sostituire la vecchia tecnologia planare.

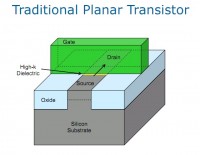

Nei modelli soprastanti notiamo la sostanziale differenza tra la struttura planare e quella tridimensionale.

Nella struttura planare vi è un passaggio di elettroni al di sotto del gate durante la fase “ON”; in questo caso la superficie di scambio è solamente una.

Nella neonata struttura tri-gate possiamo notare come l'aletta di silicio che si solleva dalla base permetta lo scambio su ben tre facce, aumentando la superficie di contatto, quindi incrementando le prestazioni.

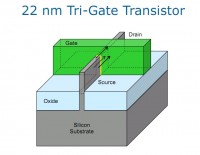

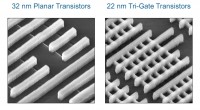

In questa immagine possiamo notare la differenza tra la “vecchia” e la “nuova” struttura.

Sulla destra, infatti, troviamo il 3D tri-gate transistor; i lineamenti più alti sono i gate, attraversati perpendicolarmente dai fin, con i contatti di drain e di source e il canale di conduzione nella parte sottostante al gate.

Per capire meglio le potenzialità del trigate rispetto alle altre tecnologie, dobbiamo considerare che la tensione di gate va ad influenzare sia lo svuotamento delle cariche in stato di off sia il passaggio di corrente nella parte del semiconduttore vicina all’ossido nello stato di on. Più il semiconduttore è lontano dalla superficie del gate e minore sarà l’influenza della tensione di gate. Per migliorare la tecnologia CMOS finora erano state adottate delle tecnologie SOI (Silicon On Insulator).

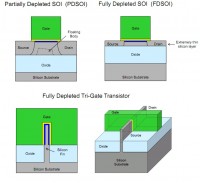

L'immagine mostra le differenze tra le varie tecnologie SOI.

La Partially Depleted SOI è una tecnologia che Intel ha deciso di non utilizzare in quanto incline ad un degrado del substrato presente all'interno della fascia di “floating body” compresa tra diossido di silicio isolante e il gate; in tale fascia si presentano residui di cariche elettroniche parassite, in quanto il gate non riesce a svuotare completamente la parte di semiconduttore più lontana

Il Fully Depleted SOI o FDSOI abbreviato, riduce notevolmente lo strato di silicone presente tra l’isolante e il gate eliminando il “floating body”; questo permette una migliore efficienza in quanto a scambio elettronico.

L’aspetto negativo di tale soluzione sono i costi di produzione; l’utilizzo della tecnologia FDSOI, con la conseguente riduzione dello strato di silicio, comporta un aumento di costi di produzione nell’ordine del 10%.

Per tale motivo Intel ha deciso di non utilizzare questa tecnologia.

La struttura Fully Depleted Tri-Gate Transistor, invece, permette un incremento di efficienza in quanto l’aletta di silicio, chiamata “fin”, parte direttamente dallo strato inferiore di silicio e si inserisce all’interno dello spazio “gate”, restando sempre vicina al contatto metallico.

Questo processo aumenta i costi di produzione di appena il 2-3% rendendo la soluzione idonea al raggiungimento degli obiettivi posti da Bohr.